Over the last 20 years, I have heard many – sometimes amusing – explanations for the double pulse. For example, “the double pulse is the characterisation of an electrical quadrupole, with the first pulse describing the input and the second pulse the output”. What is self-evident for the experienced professional can sometimes cause misunderstandings for the less experienced. As a test equipment manufacturer, realised that users have different perspectives of the topic of double pulse testing.

Dipl. Ing. Konrad Domes — CEO, SAXOGY POWER ELECTRONICS GmbH

This article appeared in Bodo’s Power Systems® Magazine – February 2024. You can download the issue here: https://www.bodospower.com/current.aspx

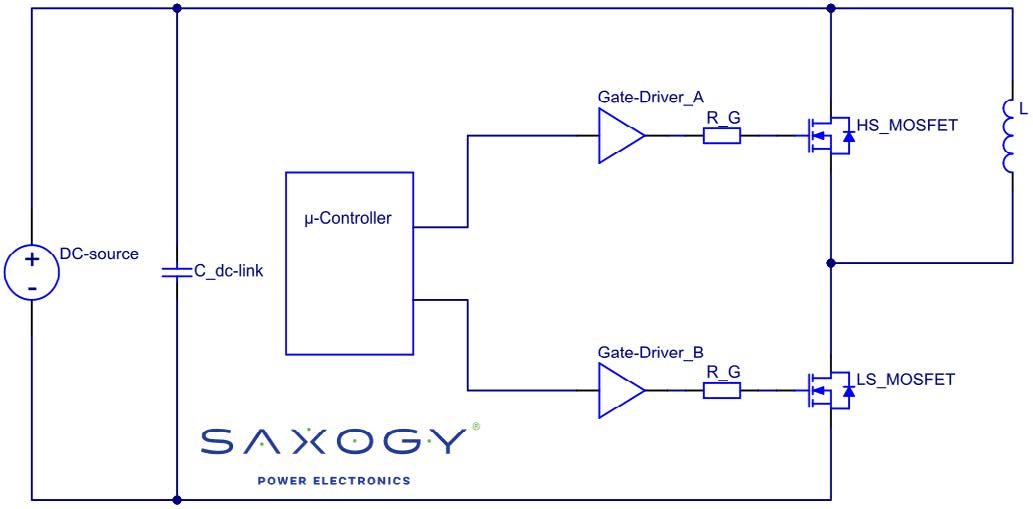

The development of a power electronic assembly requires several steps. One of these involves the dynamic characterization of the switching behaviour of the power semiconductors. For this purpose, a double-pulse test setup is used which includes:

- a capacitive energy storage device, also known as dc-link capacitor,

- the power semiconductors that are to be tested, which consist of at least one switch and one diode, and

- a load inductor, which functions as a magnetic transducer.

The IEC 60747-9 standard explains the corresponding test setup and the measurement results using the example of an IGBT. As expected, no further details are given about the real designs and possible pitfalls.

What is the double pulse actually used for?

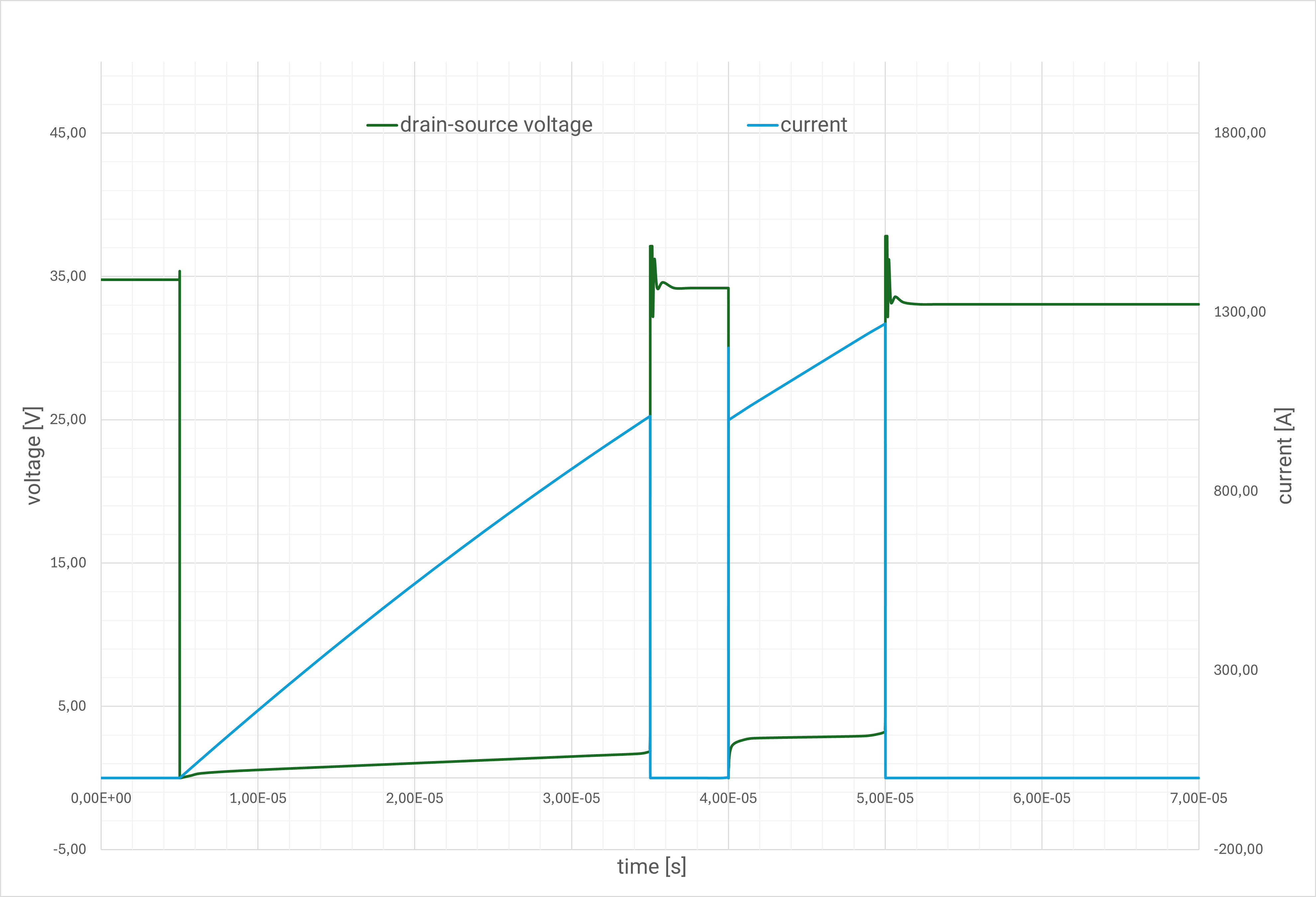

The schematic of a possible double pulse setup is displayed in picture 1, with the measurement data in picture 2.

With a first pulse, the load inductance is magnetised up to the desired rated current, whereby switching off the current provides the first data (A) on the switch-off behaviour at the operating point. After a recovery time, during which the semiconductor must be completely de-energised, it is switched on again. The previous nominal current flows – driven by the load inductance – in the opposite diode. When switched on again, the current commutates back into the semiconductor that is being tested.

This provides the second data set (B) with all the information about the turn-on behaviour of the power semiconductor. Once the turnon process under nominal current has been fully recorded, the second pulse is switched off. However, the resulting data are not necessarily of interest.

In general, it is assumed that a semiconductor that survives a switching operation at a specified operation point without any

problems, will always survive this operation point. Provided the semiconductor does not degrade and the resulting heat is continuously dissipated. The required cooling capacity can be calculated by characterising all plausible operation points and by calculating the power losses, considering the switching frequency.

Parasites – invisible but meanly

In addition to the load inductance, each piece of connecting cable introduces a further amount of inductance into the circuit. Unfortunately, this also occurs in areas where there should be as little as possible or no inductance at all. Additionally, each piece of cable forms a coupling capacitance to neighbouring conductors. These parasitic passive components in turn form resonant circuits, which can easily be triggered by fast-switching components.

Of course, all distances between the components should be as short as possible. The commutation circuit, which is formed by the two semiconductors and the dc-link capacitance, can thus be reduced to inductance values of approx. 10 nH.

After the turn-off, the corresponding semiconductor turns off by building up a junction barrier. The junction-capacitance forms a resonant circuit with the commutation inductance. The resulting turn-off oscillations can be recognised as an overlap on the reverse voltage curve. The turn-off process interrupts the current flow in the commutation inductor, causing it to generate a turn-off overvoltage.

Depending on the setup, the overlap of turn-off overvoltage and turn-off oscillation can lead to an increase or partial cancellation of the peak voltage value. To prevent the maximum reverse voltage on the semiconductor from being exceeded and the associated destruction of the semiconductor, the turn-off behaviour should be characterised under worst-case conditions. These include the use of the future target layout, the expected junction temperature with the highest switching speed and the turn-off at the highest current.

Experience shows that critical conditions sometimes occur even at operating points between the maximum values. For this reason, close characterisation of the switching processes over the entire operating range is recommended.

The right sequence saves time

Here, a fundamental distinction must be made between characterising the semiconductor and characterising the power electronics.

Load current

The easiest and fastest way to obtain data is to modify the operating point of the current. The current to be switched off is related to the turn-on time. There are two issues to be considered:

- The current-carrying load inductance has a certain energy amount that was provided by the dc-link capacitance until turn

off. - Energy was lost during the turn on phase due to conduction losses. As a result, after turn-off the dc-link capacitance no longer has the same voltage value as when it was switched on.

To switch off at a specific voltage value, the dc-link voltage must therefore be increased by the expected difference. The current range should consider all values that occur during operation – especially short circuit events.

The range between two operating points is debatable: 5 to 10 operating points within the rated current range are common. Of course, a fully automatic test bench allows a more closely meshed characterisation. Fortunately, the days when every measurement plot was saved on a disc or evaluated with a lot of manpower are long gone…

Gate configuration

Some setups offer the option of manipulating the way in which the gate driver is controlled. For example, gate resistors, gate currents or gate voltages can be adjusted automatically. As these have a direct influence on the switching behaviour, those must be considered during the characterisation. Often only seconds are needed to re-parameterise the gate driver. It is therefore recommended – after each operating point or at the end of a series of operating points with the same dc-link voltage – to include the new parameter in the characterisation.

However, if the gate driver is not automated, manual parameterisation should be carried out at the end of the entire measurement series. As the test system must be disconnected from the power supply after each pulse and the statistical number of accesses is therefore significantly higher than when parameterising a complete series, this significantly minimises the safety risk. Characterisation over the entire current range is now repeated for different dc-link voltages. To save energy and time, it is advisable to characterise several current values with the same dc-link voltage. This avoids unnecessary charging and discharging cycles of the dc-link capacitor.

Dc-link voltage

The voltage range limitations for semiconductor characterisation are between zero and usually 80% of the maximum permissible reverse voltage. The turn-off overvoltage must never exceed the maximum permissible reverse voltage!

When characterising power electronics, for example, it is possible to limit the characterisation parameters to the voltage range of the inverter. Usually, all voltage ranges are measured with at least 5 to 10 intermediate points, whereby, again, a more detailed characterisation provides more insight.

Junction temperature

The junction temperature is usually the last parameter to be modified. Several different methods are possible. The easiest way to control the temperature is to use a heating plate, where the semiconductor or the heat sink is heated up to the desired temperature. With this method, however, only junction temperatures above room temperature are possible.

An extension of the process is the temperature regulation by means of a hydraulic temperature control plate. In principle, this

is an oil-filled heat sink. The temperature of the oil is controlled by a temperature control unit. With this setup temperature ranges between -40°C and +200°C are possible. It should be noted that at temperatures below the dew point, condensation and later icing of the device under test (DUT) can occur. In turn, metallic surfaces can oxidise at high temperatures. Ideally, the DUT should be operated in an inert gas environment. The moisture and oxygen-free environment prevents both icing and oxidation.

To summarise, it can be said:

Of course, these few words can only provide a rough overview on this topic. The double pulse probably offers enough material to write an entire book. Our aim is to look at important aspects of the double pulse in more detail in the following issues. I hope that this short treatise will increase the number of double pulse engineers and that even more reliable solutions will be created in the future.

Anyone who does not feel confident enough to tackle the subject in such depth but still needs results is welcome to get in touch with us. We at SAXOGY® have a whole series of predefined solutions. If you cannot find what you are looking for, we will be happy to develop a customised solution.

Let’s work together to fully utilise the possibilities of power electronics and take your projects to a new level.